わかりにくいが、VLNV列のxilinx.com:ip:clk_wiz:6.0をダブルクリックするとウィザードが起動する。

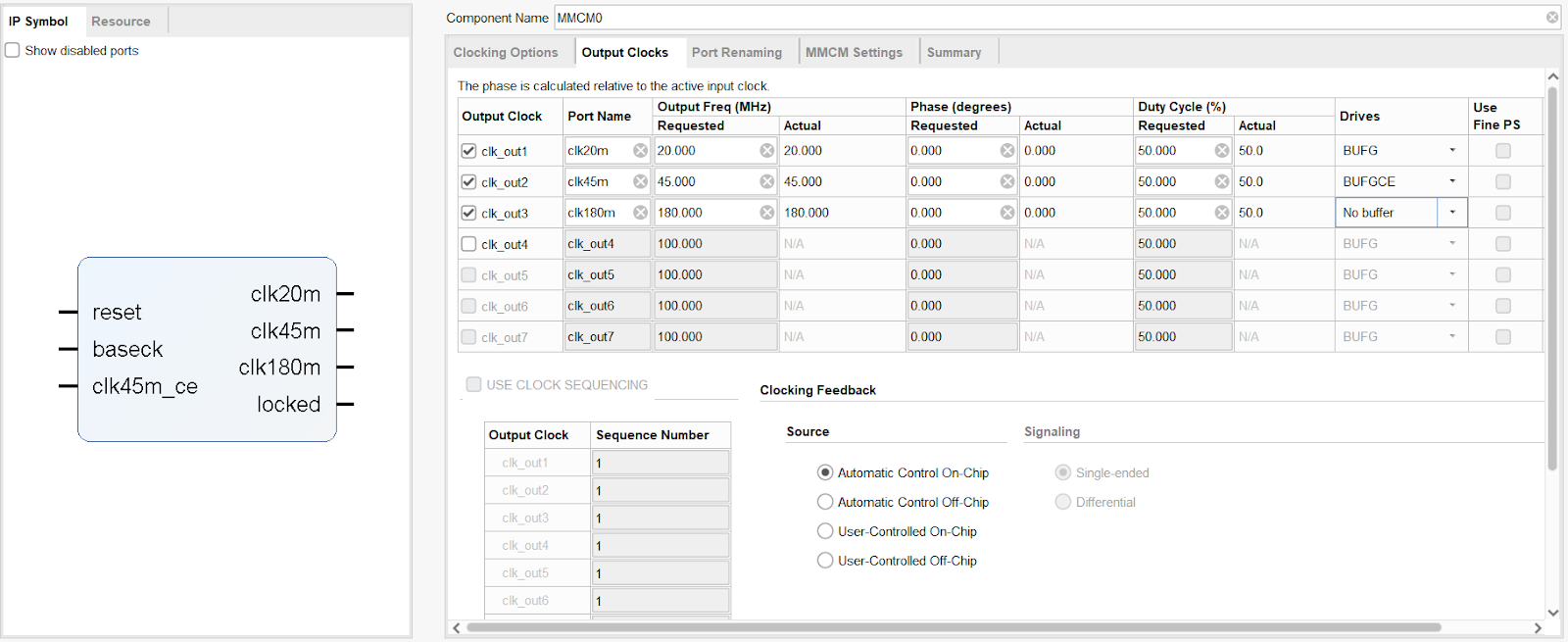

Show disabled portsのチェックボックスを外すと、使わない端子が見えなくなる。

クロックウィザードにはMMCMとPLLがある。今回はMMCMを選択する。

Input Clock Informationでソースクロックのクロック名、周波数を指定できる。

生成するクロックを指定する。20MHzのクロックを作ってみる。

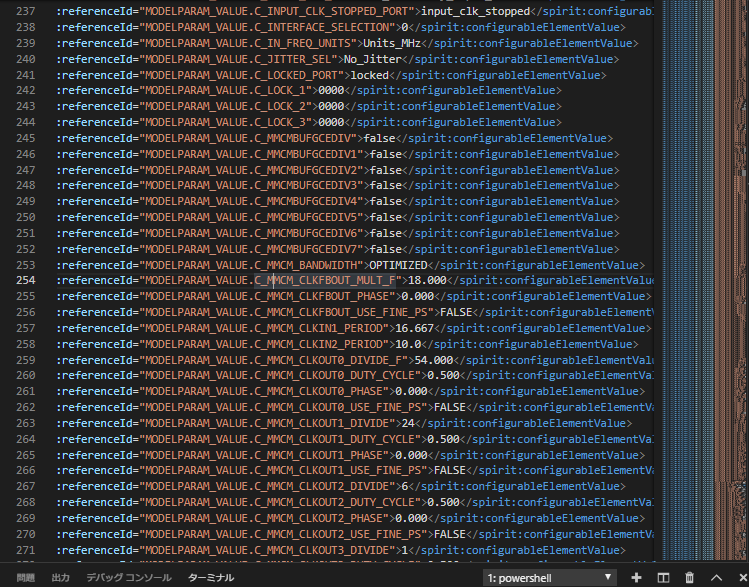

ここは自動で設定される。850となっている。これは3分周クロックを42.5逓倍した値。この値はツールが自動で決めている。

60 / 3 * 42.5 / 42.5 = 20MHzという計算になる。なぜ42.5なのかは不明。あくまでツールが都合の良い値を自動で設定している。

さらに45MHzを追加すると、60 * 16.5 (=990) / 22 = 45MHzという計算になる。

さらに180MHzを追加する。

60 * 18 (=1080) / 6 = 180MHzという計算になる。

続いてバッファータイプの指定をする。デフォルトはBUFG(BUFGCTRL)。

20MHzはそのままBUFG、45MHzはBUFGCE(停止制御付き)、180MHzはローカルインターコネクト(非推奨)としている。

続いてここまでのサマリーを確認する。

最終的にMultiplyは18となったので、20MHz,45MHzもそれに合わせたM/D数に変更されている。

この条件でIPを作成する。

Out of Contextで生成。

Globalはプロジェクトモード。プロジェクトをコンパイルする際にIPも毎回コンパイルする。

Out of ContextではIPはIPのネットリストとして独立し、プロジェクトのコンパイル時には再コンパイルせずにネットリストを使用する。

MMCM0.vは作成したIPをインスタンスする際のサンプルになっている。

MMCM0_stub.vは、MMCM0をvivado以外のコンパイラで使う際のブラックボックスモジュール。vivadoではxciファイルをプロジェクトに読み込んでいれば自動で認識される。

MMCM0.xciはvivadoで使われるMMCM0モジュール本体。xmlフォーマットで全てのマクロ情報を含んでいる。

0 件のコメント:

コメントを投稿