ISEのCore Generator相当はvivadoでManage IPとなっている。

Common Clock Builtin FIFOを使う。

First Word Fall Through(FWFT)モードにする。REと同時にリードデータが出力され、レイテンシ0となるモード。

FIFOのサイズは32bit×512Byte (4KByte空間)とする。

リセットは同期リセットとする。

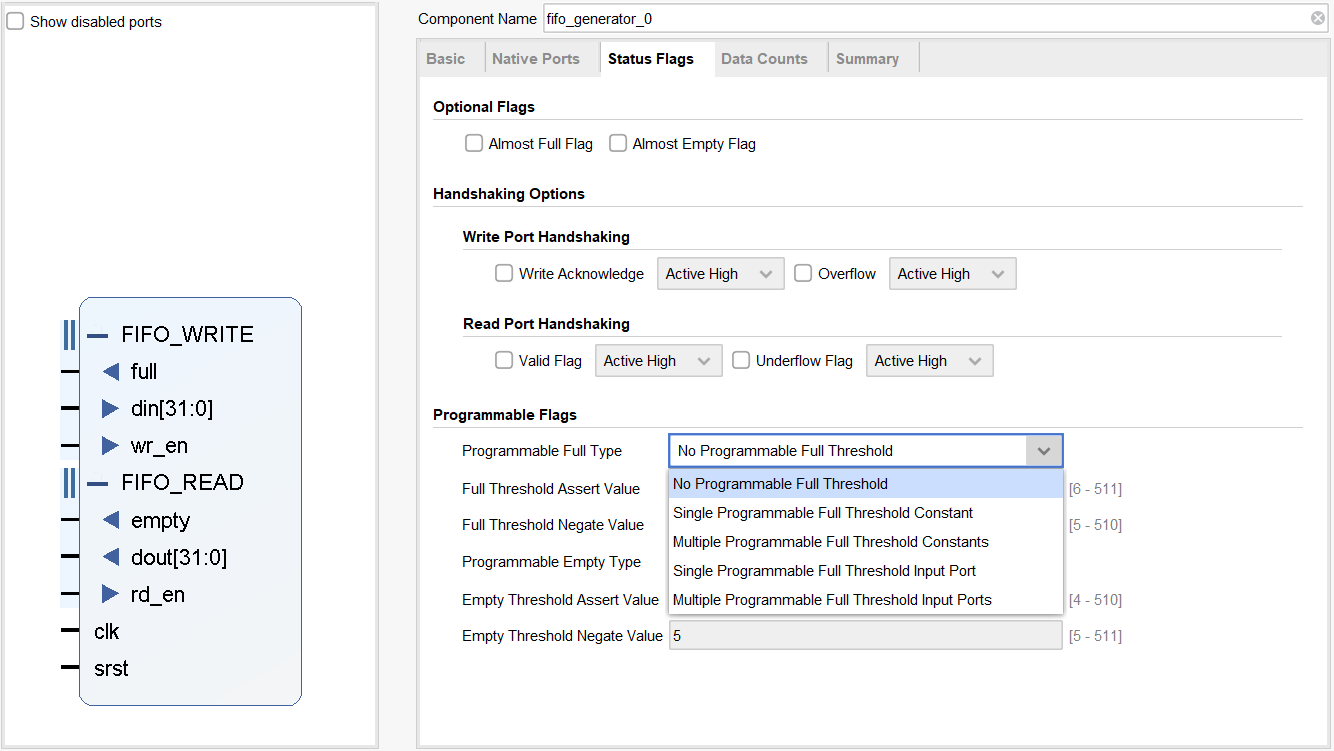

FFIOの端子は最小でclk, srst(オプション), full, din, wr_en, empty, dout, rd_en。

fullとemptyは任意にスレッショルドを設定できる。

”Multiple Programable Full Threshold Input Port”は、ポートでドライブされた値によってprog_full信号をアサートするタイミングを決める。

"Full Threshold Assert Value", "Full Threshold Negative Value"が自動で入力されるが、(ポート設定モードなので)グレーアウトされていて入力できない(設定不可)。代わりにprog_full_thresh_assert、prog_full_thresh_negate端子が追加される。

Emptyは”Single Programmable Empty Threshold Constant”を使ってみる。

"Empty Threshold Assert Value"のみ入力可能で、Empty Threshold Negate Valueはグレーアウトされている。prog_emptyの閾値はポート設定ではなく、固定値としてカプセル化される。

アドレスを出力することも可能。 (Data Count)

サマリーをチェックする。

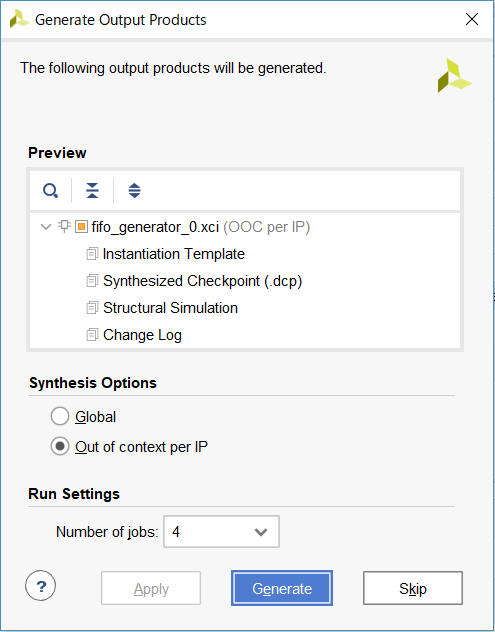

Generateする。

Progress=100%で生成完了。

fifo_generator_0_stub.vは外部ツールでコンパイルする際のブラックボックスモジュールとして使う。

xciファイルはxml形式のファイルで、すべての情報を含んでいる。

0 件のコメント:

コメントを投稿